# Da Yu Hohyung Lee Seungbae Park<sup>1</sup>

Department of Mechanical Engineering, State University of New York at Binghamton, P.O. Box 6000, Binghamton, NY 13902

# Reliability Assessment of Preloaded Solder Joint Under Thermal Cycling

The ever increasing power density in modern semiconductor devices requires heat dissipation solution such as heat sink to remove heat away from the device. A compressive loading is usually applied to reduce the interfacial thermal resistance between package and heat sink. In this paper, both experimental approaches and numerical modeling were employed to study the effect of compressive loading on the interconnect reliability under thermal cycling conditions. A special loading fixture which simulated the heat sink was designed to apply compressive loading to the package. The JEDEC standard thermal cycle tests were performed and the resistance of daisy chained circuits was in situ measured. The time to crack initiation and time to permanent failure were identified separately based on in situ resistance measurement results. Failure analysis has been performed to identify the failure modes of solder joint with and without the presence of compressive loading. A finite element based thermal-fatigue life prediction model for SAC305 solder joint under compressive loading was also developed to understand the thermal-fatigue crack behaviors of solder joint and successfully validated with the experimental results. [DOI: 10.1115/1.4007674]

### Introduction

Root causes of electronic package failure can be classified as drop impact [1–3], vibration [4,5], thermal cycling [6–9], etc. As thermal loading appears to be the major cause of electronic component failures, the majority of research work focus on the failure mechanisms and fatigue life prediction models of solder interconnect under thermal loading. However, as the heat sink is widely used to dissipate the heat in the field-use conditions, the electronic package is often exposed to the thermal compression loads during its service life. The preload effect on the thermal-fatigue performance of solder joint becomes a critical reliability issue.

Solder collapse, which leads to electrical shorting by bridging to adjacent solder joints, and solder joint fatigue crack were identified as two failure modes for the preloaded solder joints under thermal cycling [10]. A higher compressive loading is desirable as it reduces the interfacial thermal resistance between package and heat sink and increases heat dissipation efficiency. However, more creep collapse and bridging of solder joints are expected to happen [11]. Chiu et al. characterized the responses of solder joints to compressive load and model the corresponding failure. The compressive creep behavior of Sn3.8Ag0.7Cu solder was investigated. A viscoplastic constitutive model developed from the creep characterization was then incorporated into finite element analysis (FEA) to predict solder joint creep collapse and bridging under heat sink compressive load. Zhang [12] performed modeling and testing a flip chip HITCE BGA package in a system setting with a heat sink on top of the HITCE package. According to the simulation results, increasing the heat sink load will create more damage in the solder bumps, however, lowers the damage of solder balls. Bhatti et al. [13] evaluated the reliability of solder joints in the presence of a preload. 3D nonlinear finite element analysis is performed to simulate the effect of compressive load in thermal cycling. Garner et al. [14] provided an understanding of the compressive load effect and new methods to characterize the limits of compressive loads for reliable operation throughout the life of the component.

So far the effect of compressive loading on the solder joint thermal-fatigue life is not thoroughly investigated in terms of failure modes and failure mechanisms, and finite element based prediction model is not well defined and validated. In this paper, the effect of heat sink induced preload on thermal-fatigue life of SAC305 solder joint was investigated through thermal cycling testing. A loading fixture was developed to apply compression load to the BGA package uniformly. The standard JEDEC thermal cycle condition was applied to test vehicles. Cross section polishing was performed to identify the associated failure modes. An accurately validated numerical model has been developed as an invaluable tool for analysis of thermal-fatigue crack behaviors and subsequent fatigue life prediction.

# **Test Vehicle and Experimental Setup**

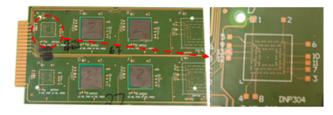

Four 92BGA packages,  $27 \, \text{mm} \times 27 \, \text{mm}$ , mounted with  $0.6 \, \text{mm}$  diameter and  $0.3 \, \text{mm}$  height lead-free solder balls (SAC305) in  $1.8 \, \text{mm}$  pitch were assembled on a  $1.6 \, \text{mm}$  thick PCB (see Fig. 1). The large-pitch between solder joints was specially designed to eliminate the potential bridging between adjacent solder joints due to the solder joint collapse. Only solder joint fatigue crack could be observed in the failed test vehicles. The resistance of built-in daisy chained circuits was monitored constantly throughout the test and the failure time was recorded accordingly.

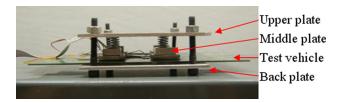

A special fixture was designed to apply compression load to the package (see Fig. 2). The test vehicle was clamped between the aluminum made middle and back plates with four springs placed

Fig. 1 Test vehicle with four 92BGA packages attached and daisy chained circuits of 92BGA

**Journal of Electronic Packaging**

Copyright © 2012 by ASME

DECEMBER 2012, Vol. 134 / 041008-1

<sup>\*</sup>Corresponding author.

Contributed by the Electronic and Photonic Packaging Division of ASME for publication in the JOURNAL OF ELECTRONIC PACKAGING. Manuscript received June 12, 2012; final manuscript received September 5, 2012; published online November 16, 2012. Assoc. Editor: Bongtae Han.

Fig. 2 Compressive load fixture

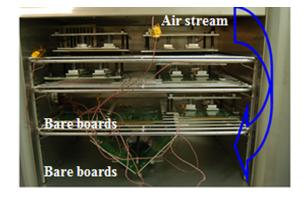

Fig. 3 Thermal chamber setup with air stream flowing from upper right corner to upper left corner

in between the upper and middle plates. In order to apply the compression load uniformly, the low stiffness springs with similar size of middle plate were placed at the middle plate center. 8 lb. compressive load controlled by the amount of spring compression was

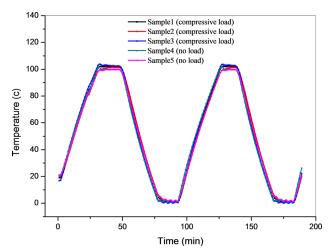

Fig. 4 Temperature cycling profiles of all test boards

applied to each BGA package. Thermal interface material was used between contact surfaces of the middle plate and package to enhance thermal conduction and reduce friction.

# **Thermal Cycling Test**

Three test boards assembled on the compressive load fixtures and two bare test boards without any external loading were subjected to the specified temperature cycling test profile. The standard JEDEC temperature cycling profile [15] consists of 30 min ramp up and down between 0 °C to 100 °C, 15 min dwell at the

Fig. 5 A typical resistance measurement result of the whole test period

041008-2 / Vol. 134, DECEMBER 2012

Transactions of the ASME

two extreme temperature (0  $^{\circ}$ C and 100  $^{\circ}$ C), respectively, which is 1.5 h per cycle in total.

A slightly benign thermal excursion profile for solder joints in cases with big heat sink than that without a heat sink may lead to the thermal reliability improvement of interconnects [10]. Therefore, a uniform thermal profile should be obtained to eliminate this effect. A great effort has been made to achieve the same temperature cycling profile to all test vehicles by minimizing the thermal mass of loading fixture and placing the bare test boards at worst-case temperature locations (see Fig. 3). Five thermocouples were placed on one of packages of each test board. It is clearly shown that a uniform temperature cycling profile is achieved to all test boards in Fig. 4.

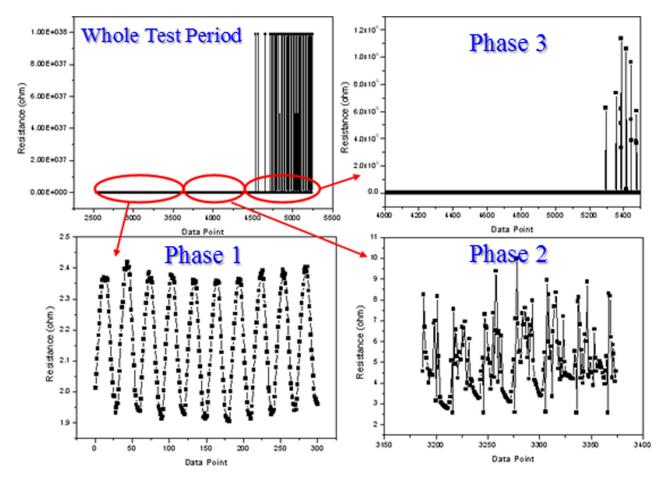

Data acquisition system was used to monitor the daisy-chain resistance and temperature cycling profile in situ. A typical resistance measurement result of the whole test period is plotted in Fig. 5. The whole test period can be divided into three phases based on the resistance value fluctuation. The majority of whole test period, which has a stable resistance value fluctuation due to the temperature cycling fluctuation, is defined as the phase 1. As the crack initiates and propagates in the solder joints, the phase 2 has a larger and random resistance value fluctuation. The phase 3 corresponds to resistance value spiking (more than  $1000~\Omega$ ) due to the complete crack in the solder joint and indicates permanent failure of solder joint.

According to the IPC-9701 specification [16], a "failure event" was recorded if the resistance of a channel exceeded its initial value by 20% within a maximum of five consecutive reading scans. Therefore, the beginning of phase 2 is defined as time to crack initiation in this work by following the IPC-9701 specification. However, as the phase 3 represents the complete crack in the solder joint, time to permanent failure is defined as the resistance exceeded 1000  $\Omega$  within a five consecutive reading scans and is also investigated in this work.

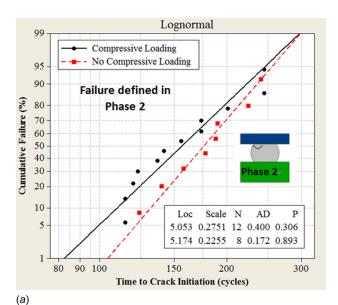

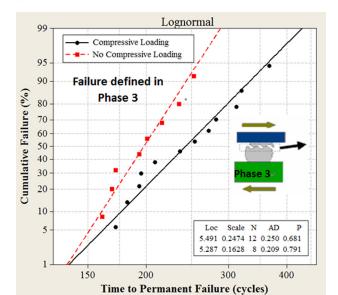

Failure data of time to crack initiation (phase 2) and time to permanent failure (phase 3) from temperature cycling tests were plotted using a lognormal distribution model as shown in Figs. 6(a) and 6(b).

In this test, the mean time to crack initiation of solder joint with and without compressive loading are 157 and 177, respectively (Fig. 6(a)), which is consistent with other research work [17], indicating compressive loading has a detrimental effect on the thermal-fatigue reliability of solder joints. However, it is clearly shown in Fig. 6(b) that the compressive loading increases the permanent failure time of preloaded solder joints by 23% (Table 1). Failure analysis and finite element analysis are needed to understand the failure mechanisms and thermal-fatigue induced crack behaviors of preloaded solder joints.

# **Failure Analysis**

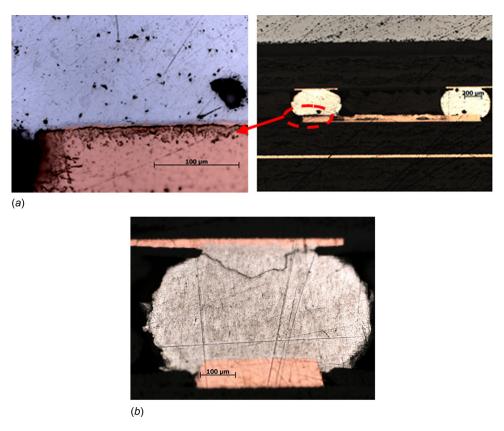

Cross section polishing was performed for the failure analysis. Failure locations were identified to be the package outmost corners which were also under the die periphery for both cases with and without compressive load.

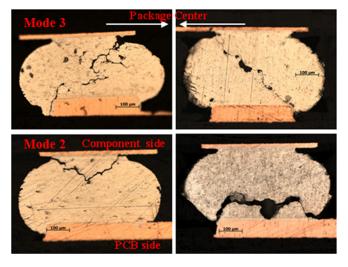

The solder joints without preload show typical fatigue crack propagated through the intermetallic compound (IMC) layer (defined as mode 1) (see Fig. 7(a)) or through Cu pad/solder interface which is close to the IMC layer (defined as mode 2) (see Fig. 7(b)).

It is clearly indicated that the crack propagation path changed accordingly in all failed packages as the compression applied. As shown in Fig. 8, two failure modes were identified: crack propagated through Cu pad/solder interface which is defined as mode 2 described above, diagonal fracturing through the bulk of solder joint, which is defined as mode 3.

The statistics of each failure mode was summarized in Table 2. Apparently, crack propagated through the Cu pad/solder interface is still the dominant failure mode as observed in 66.7% of failed samples. However, mode 3 is only observed in the preloaded sol-

Fig. 6 (a) Lognormal distribution of time to crack initiation and (b) lognormal distribution of time to permanent failure

Table 1 Thermal cycle test results

|                                | With preload | Without preload |

|--------------------------------|--------------|-----------------|

| Mean time to crack initiation  | 157          | 177             |

| Mean time to permanent failure | 243          | 198             |

der joints. Moreover, all failed solder joints were more frequently found to have crack along the Cu pad/solder interface on the component side than on the PCB side.

### **Finite Element Model**

(b)

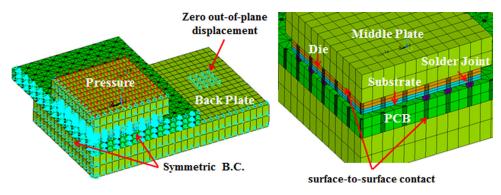

FEA was performed with the commercial software ANSYS 13 for the analysis of thermal-fatigue crack behaviors and fatigue life prediction. In this FEA model, only the corner solder joints were modeled in detail and fine meshed, where the thermal-fatigue failure is always expected to occur due to the largest distance to neutral point (Fig. 9).

**Journal of Electronic Packaging**

DECEMBER 2012, Vol. 134 / 041008-3

Fig. 7 (a) Crack propagated through the IMC layer (mode 1) (b) crack propagated through Cu pad/solder interface (mode 2)

Fig. 8 Two failure modes of failed packages with the presence of compressive load

Table 2 Statistics of failure mode

|                 | Failed samples | Mode 1 (%) | Mode 2 (%) | Mode 3 (%) |

|-----------------|----------------|------------|------------|------------|

| With preload    | 12             | 0          | 66.7       | 33.3       |

| Without preload | 8              | 37.5       | 62.5       | 0          |

All materials were assumed to be linear elastic except solder joint (see Table 3), which was considered as a viscoplastic material. Anand's viscoplastic constitutive model was used for the solder joint. Solder joint was modeled with VISCO107 element while the rest of assembly in the model was modeled with SOLID45.

Two surface-to-surface contacts were defined along middle plate to top surface of die interface and bottom of PCB to back plate interface, as components can slide at these interfaces. Symmetry boundary conditions were applied to the cut-planes of the quarter symmetry model. The out-of-plane displacement was also constrained to the corner of back plate where the bolt connected as boundary condition. Uniform pressure was applied to the top surface of middle plate to prestress the solder joints.

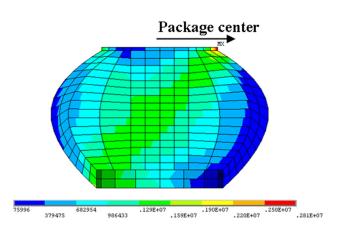

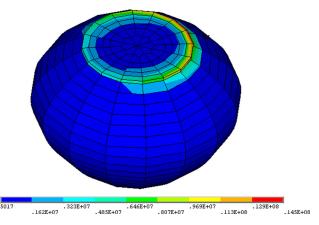

Figure 10 shows the Von Mises stress contour plot of the corner solder joint under the compressive load. According to the static analysis result, the corner solder joint has stress concentration along its diagonal, which might lead to the diagonal fracturing of solder joint during temperature cycling.

041008-4 / Vol. 134, DECEMBER 2012

Transactions of the ASME

Fig. 9 Finite element model of the test assembly

Table 3 Material properties

| Materials       | Young's modulus<br>(GPa) | Poisson's ratio | CTE<br>(ppm/C) |

|-----------------|--------------------------|-----------------|----------------|

| PCB             | 32                       | 0.28            | 20             |

| Substrate       | 17                       | 0.28            | 15             |

| Die             | 131                      | 0.30            | 3              |

| Cu pad          | 129                      | 0.34            | 17             |

| Aluminium plate | 68                       | 0.36            | 25             |

Fig. 10 Von Mises stress contour plot of the corner solder joint under compressive loading

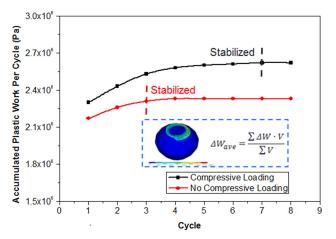

The volume-averaged plastic work per cycle over the elements along the solder joint interface, as well known in Darveaux's model, is used as a metric to assess solder joint reliability in this work. As solder joints continue to creep under compressive loading, the accumulated plastic work per cycle stabilizes after seven cycles while it stabilizes within only three cycles without preload (Fig. 11). The data reported in the subsequent analysis are the stabilized accumulated plastic work per cycle.

As shown in Fig. 12, the maximum plastic work occurs at the corner solder joint along the Cu pad/solder interface, which correlates well with the dominant failure mode.

In this paper, Darveaux's model is employed to correlate the fatigue life with the accumulated plastic work per cycle. In Darveaux's model, the fatigue life consists of the crack initiation and the crack growth.

The number of cycles before crack initiation N<sub>0</sub> is calculated as

$$N_0 = K_1 \Delta W_{\text{ave}}^{K_2} \tag{1}$$

The crack growth rate per cycle da/dN is calculated as

$$\frac{da}{dN} = K_3 \Delta W_{\text{ave}}^{K_4} \tag{2}$$

Fig. 11 Accumulated plastic work per cycle

Fig. 12 Solder joint plastic work distribution

Therefore, the total number of cycles before failure,  $N_a$  can be written as

$$N_a = N_0 + \frac{a}{da/dN} \tag{3}$$

Where  $\Delta W_{\text{ave}}$  is the accumulated plastic work per cycle,  $K_1$ ,  $K_2$ ,  $K_3$ , and  $K_4$  are constants, and a is the crack length (total distance the crack propagated before permanent failure). In this work, the mean value of examined cracks in all failed solder joints is defined as crack length in the Darveaux's model (see Table 4).

According to the FEA predication results (Table 4), compressive load slightly increases the accumulated plastic work per cycle

DECEMBER 2012, Vol. 134 / **041008-5**

Table 4 FEA predication results

| Preload | Crack length (a) (μm) | $\Delta W$ (MPa) | $N_0$ (cycles) | Time to crack initiation (cycles) | $N_a$ (cycles) | Time to permanent failure (cycles) |

|---------|-----------------------|------------------|----------------|-----------------------------------|----------------|------------------------------------|

| Yes     | 520                   | 2.62             | 101            | 157                               | 254            | 243                                |

| No      | 356                   | 2.33             | 114            | 177                               | 226            | 198                                |

by 12%; therefore the time to crack initiation is reduced as shown in Eq. (1), in agreement with experimental results. However, a considerable increase (46%) in crack length (a) for preloaded solder joints compensates for the increase of the crack growth rate (13%), which is directly related to accumulated plastic work per cycle. As a consequence, both crack propagation time and time to permanent failure ( $N_a$ ) increase.

#### **Conclusions**

In this work, compressive loading was found to have a detrimental effect on the thermal-fatigue reliability of solder joints as a shorter crack initiation time. In the meantime, as the crack length increases significantly due to crack propagation path changed in the preloaded solder joint, crack propagation time increases although more plastic work accumulated per thermal cycle. Therefore, time to permanent failure increases for preloaded solder joints. Failure analysis has shown that crack propagated through Cu pad/solder interface is still the dominant failure mode for both cases. However, diagonal fracturing through the bulk of solder joint is only observed in the preloaded packages. Finite element analysis was performed to verify experimental results with proper boundary conditions. Energy-based prediction model, Darveaux's model, can still be employed to estimate the thermal-fatigue life of solder joint with the presence of compressive loading.

# References

- Yu, D., Kwak, J. B., and Park, S. B., 2010, "Dynamic Responses of PCB Under Product-Level Free Drop Impact," Microelectron. Reliab., 50, pp. 1028–1038

- [2] Yu, D., Kwak, J. B., and Park, S. B., 2009, "Effect of Shield-Can Design on Dynamic Responses of PCB Under Board Level Drop Impact," Proceedings of ASME-IMECE 2009, ASME Paper No. IMECE2009-12639, pp. 305–310.

- [3] Yu, D., Kwak, J. B., Park, S. B., Chung, S., and Yoon, J.-Y., 2012, "Effect of Shield-Can on Dynamic Response of Board-Level Assembly," J. Electron. Packag., 134(3), p. 031010.

- [4] Yu, D., Abdullah, A.-Y., Tung T. N., Seungbae, P., and Soonwan, C., 2011, "High-Cycle Fatigue Life Prediction of Lead-Free Solder Joints Under Random Vibration Loading," Microelectron. Reliab., 51, pp. 649–656.

- [5] Yu, D., Abdullah, A.-Y., Park, S. B., and Chung, S., "Finite Element Based Fatigue Life Prediction for Electronic Components Under Random Vibration Loading," Proceedings of the 60th Electronic Components and Technology Conference, Las Vegas, NV, June 1–4, pp. 188–193.

- [6] Dishongh, T., Basran, C., Cartwrght, A. N., Ying, Z., and Heng, L., 2002, "Impact of Temperature Cycle Profile on Fatigue Life of Solder Joints," IEEE Trans. Adv. Packag., 25(3), pp. 433–438.

- [7] Vandevelde, B., Gonzalez, M., Limaye, P., Ratchev, P., and Beyne, E., 2007, "Thermal Cycling Reliability of SnAgCu and SnPb Solder Joints: A Comparison for Several IC-Packages," Microelectron. Reliab., 47, pp. 259–265.

- [8] Kwak, J. B., Yu, D., Nguyen, T. T., and Park, S., 2011, "Solder Joint Reliability in Underfilled Flip Chip Package With a Consideration of Chip-Package-Interaction (CPI)," Proceedings of ASME-InterPACK 2011, Portland, OR, July 6–8, ASME Paper No. IPACK2011-52233, pp. 307–316.

- [9] Yu, D., Nguyen, T., Lee, H. H., Goo, N., and Park, S. B., 2011, "Effect of Compressive Loading on the Interconnect Reliability Under Thermal Cycling," Proceedings of ASME-InterPACK 2011, Portland, OR, July 6–8, ASME Paper No. IPACK2011-52232, pp. 603–608.

- [10] Chiu, T., Edwards, D., and Ahmad, M., 2010, "Ball Grid Array Solder Joint Reliability Under System Level Compressive Load," IEEE Trans. Device Mater. Reliab., 10(3). pp. 324–337.

- [11] Chiu, T. C., Lin, J.-J., Yang, H.-C., and Gupta, V., 2010, "Reliability Model for Bridging Failure of Pb-Free Ball Grid Array Solder Joints Under Compressive Load," Microelectron. Reliab., 50, pp. 2037–2050.

- [12] Zhang, R., "Characterization of Board Level Reliability of a System With Flip Chip HITCE BGA Package Through Modeling and Testing," 58th Electronic Components and Technology Conference, Lake Buena Vista, FL, May 27–30, pp. 1438–1444.

- [13] Bhatti, P. K., Pei, M., and Fan, X., "Reliability Analysis of SnPb and SnAgCu Solder Joints in FC-BGA Packages With Thermal Enabling Preload," 56th Electronic Components and Technology Conference, San Diego, CA, May 30–June 2, pp. 601–606.

- [14] Garner, L., Zhang, C., Beh, K. S., Helms, K., and Tan, Y. L., 2004, "Effect of Compression Loads on the Solder Joint Reliability of Flip Chip BGA Packages," 54th Electronic Components and Technology Conference, Las Vegas, NV, June 1–4, pp. 692–698.

- [15] JEDEC Solid State Technology Association, 2005, Temperature Cycling, JESD22-A104C, JEDEC Solid State Technology Association, Arlington, VA.

- [16] IPC, 2002, Performance Test Methods and Qualification Requirements for Surface Mount Solder Attachments, IPC 9701, IPC–Association Connecting Electronics Industries, Bannockburn, IL.

- [17] Eyman, L. M., and Kromann, G. B., 1997, "Investigation of Heat Sink Attach Methodologies and the Effects on Package Structural Integrity and Interconnect Reliability of the 119-Lead Plastic Ball Grid Array," Proceedings of the 47th Electronic Components and Technology Conference, San Jose, CA, May 18–21, pp. 1068–1075.