# Bandpass Sampling

### Proakis & Manolakis 6.4

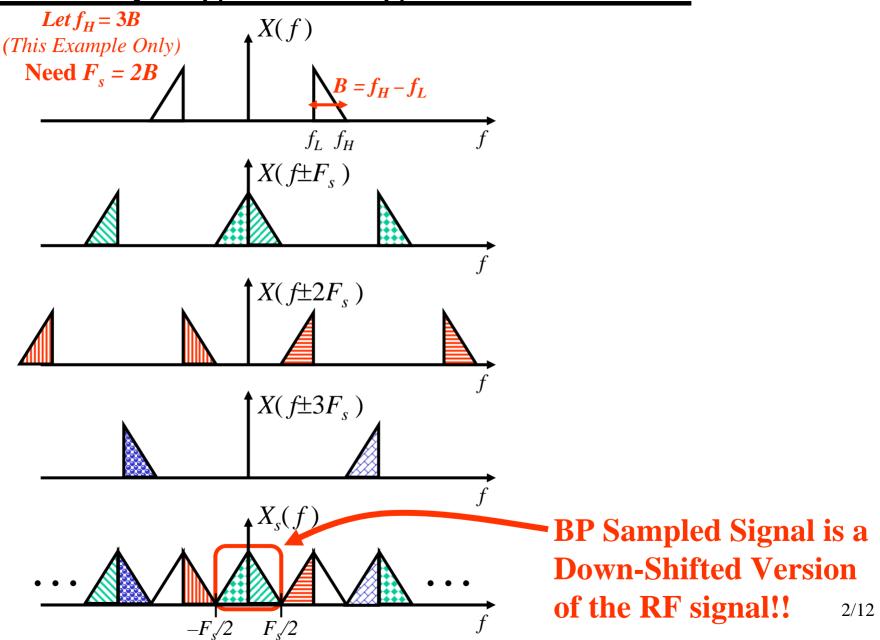

### **BP-Sampling of RF Signals: Basic Idea**

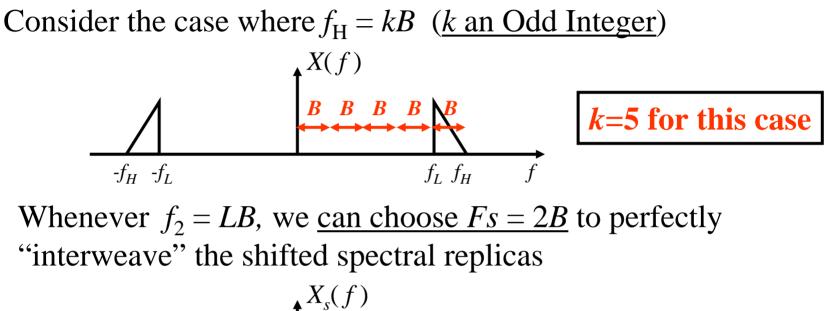

## **<u>BP-Sampling: Simple Case</u>** ( $f_{\rm H} = kB$ , *k* integer)

## **BP-Sampling: Simple Case (Cont.)**

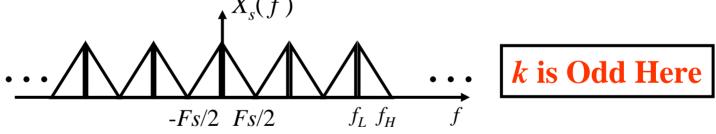

Whenever  $f_{\rm H} = LB$ , we <u>can choose Fs = 2B</u> to perfectly "interweave" the shifted spectral replicas

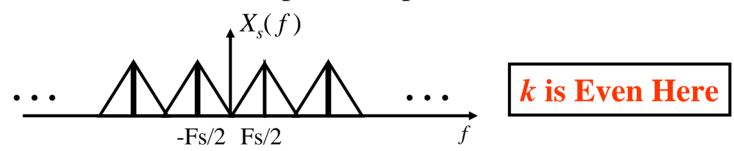

<u>Note</u>: If *k* is EVEN the spectrum in the 0 to Fs/2 range is flipped. This is not usually a problem since the next step after BP sampling is usually to create the lowpass equivalent signal, which can be done in a way that gives either spectral orientation.

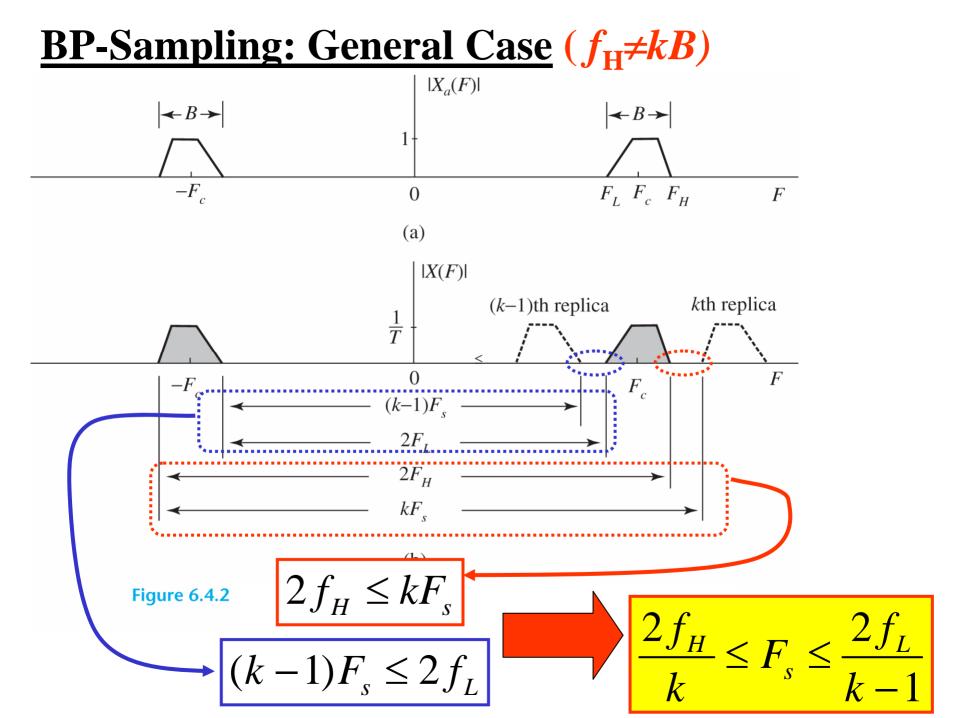

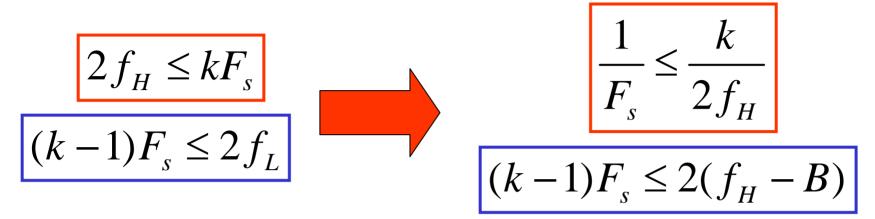

### To find the required value of *k*... re-write as:

Now... solving these for *k* gives:

**Resulting conditions needed for aliasing-free BP Sampling:**

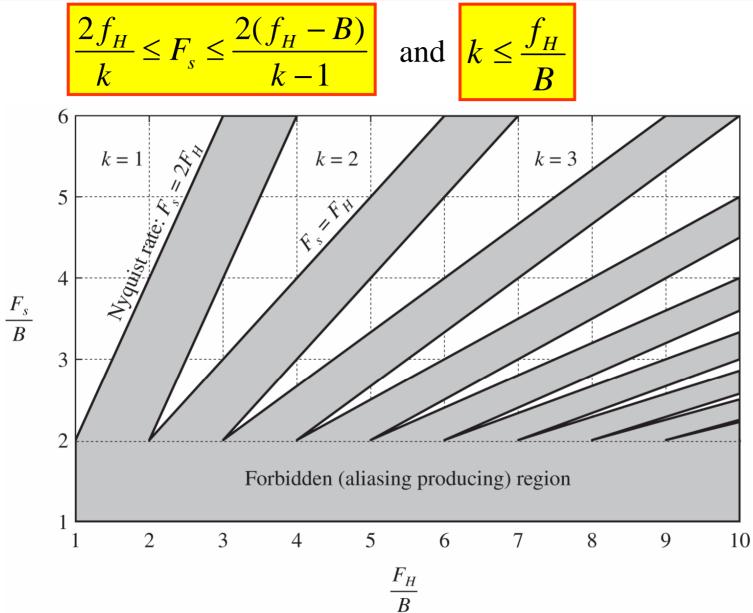

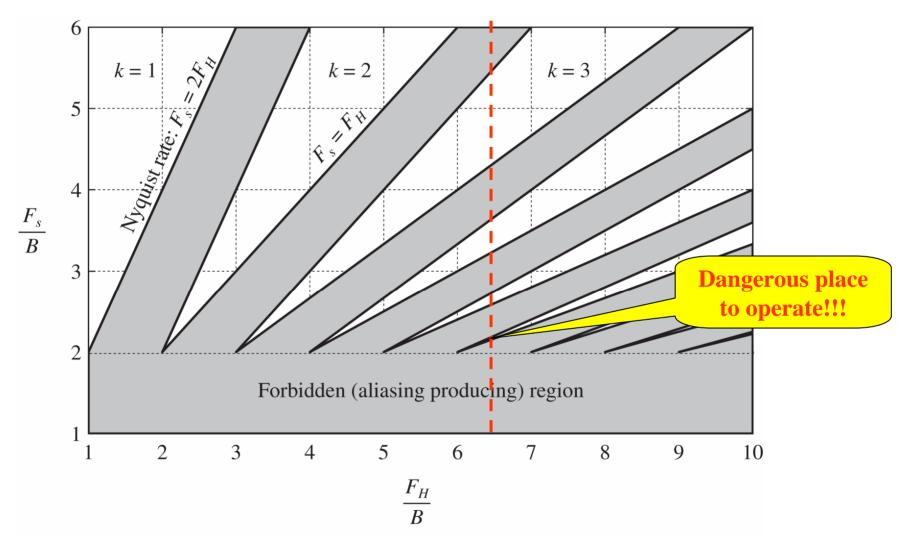

Figure 6.4.3 Allowed (white) and forbidden (shaded) sampling frequency

#### **Using Plot to Visualize Allowed Fs...**

Given  $f_H$  and  $B_{...}$  draw vertical line at  $f_H/B$

**Figure 6.4.3** Allowed (white) and forbidden (shaded) sampling frequency

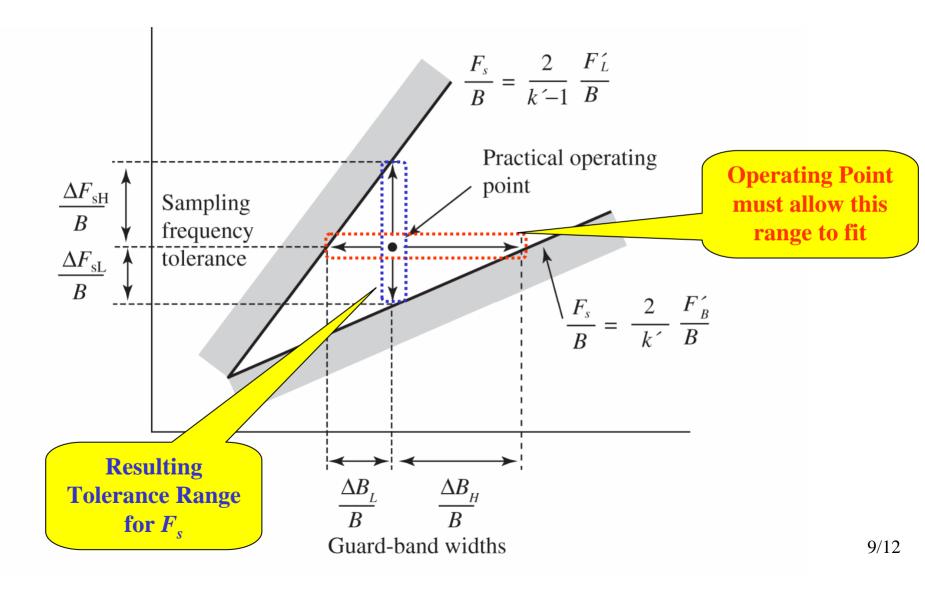

**Using Guard Band Idea to Ease Sensitivity to "Change"**

$$f'_L = f_L - \Delta B_L$$

$f'_H = f_L + \Delta B_H$   $B' = B + (\Delta B_L + \Delta B_H)$

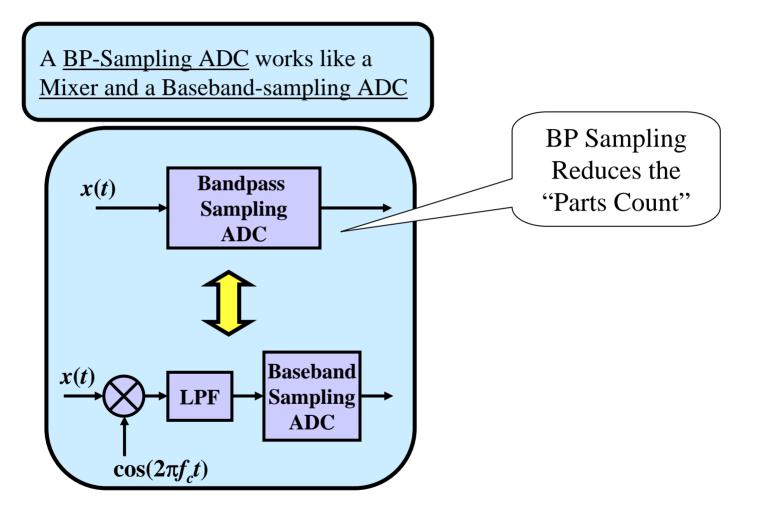

## **Advantage of BP Sampling**

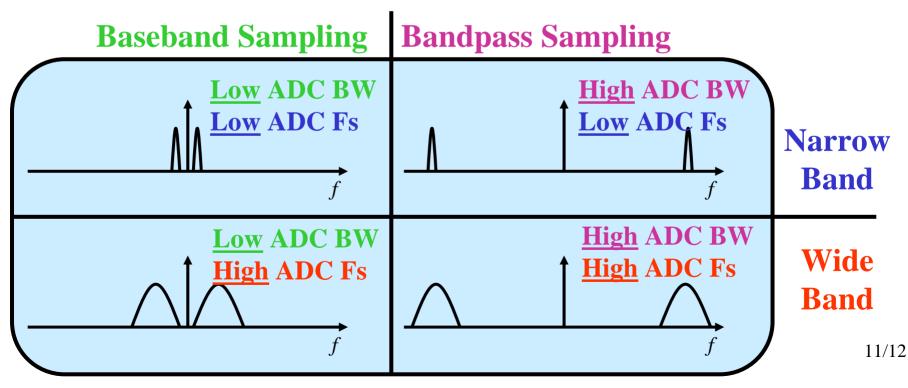

# ADC Specs: Sample Rate & ADC BW

- Sampling Rate

- <u>Fastest Rate</u> at which the ADC can be run

- Determines the <u>Widest Signal Bandwidth</u> that ADC can handle

- ADC Bandwidth

- <u>Highest Frequency</u> that ADC's internal electronics can pass

- Determines <u>Frequency Band</u> ADC can handle (e.g. HF, UHF, VHF, etc.)

- Crucial for Undersampling Applications

# WWW.harris.com

# HI5702

February 1995

#### Features

- 40 MSPS Sampling Rate  $ADC's F_s$

- 8.3 Bits Guaranteed at f<sub>IN</sub> = 10MHz

- Low Power

- Wide 250MHz Full Power Input Bandwidth

- Sample and Hold Not Required

- Single-Ended or Differential Input

- 1.25V Input Signal Range

- Single +5V Supply Voltage

- TTL Compatible Interface

- Evaluation Boards Available (HI5702-EV, HI5702-EV2)

#### Applications

- Professional Video Digitizing

- Medical Imaging

- Digital Communication Systems

- High Speed Data Acquisition

10-Bit, 40 MSPS A/D Converter

#### Description

ADC's

BW

The HI5702 is a monolithic, 10-bit, analog-to-digital converter fabricated in Harris's HBC10 BiCMOS process. It is designed for high speed applications where wide bandwidth and low power consumption are essential. Its 40 MSPS speed is made possible by a fully differential pipeline architecture which also eliminates the need for an external sample and hold circuit. The HI5702 has excellent dynamic performance while consuming <650mW power at 40 MSPS. Data output latches are provided which present valid data to the output bus with a latency of 7 clock cycles.

#### **Ordering Information**

| PART<br>NUMBER | SAMPLE<br>RATE | TEMPERATURE<br>RANGE | PACKAGE                  |

|----------------|----------------|----------------------|--------------------------|

| HI5702KCB      | 40 MSPS        | 0°C to +70°C         | 28 Lead Plastic SOIC (W) |

| HI5702JCB      | 36 MSPS        | 0°C to +70°C         | 28 Lead Plastic SOIC (W) |